### 7. SUBJECT DETAILS

### 7.5 ELECTRONIC DEVICES AND CIRCUITS

- 7.5.1 Objectives and Relevance

- 7.5.2 Scope

- 7.5.3 Prerequisites

- 7.5.4 Syllabus

- i. JNTU

- ii. GATE

- iii. IES

- 7.5.5 Suggested Books

- 7.5.6 Websites

- 7.5.7 Experts's Details

- 7.5.8 Journals

- 7.5.9 Findings and Developments

- 7.5.10 Session Plan

- 7.5.11 Question Bank

- i. JNTU

- ii. GATE

- iii. IES

#### 7.5.1 OBJECTIVES AND RELEVANCE

The primary objective of this subject is to get a clear picture of the internal physical behavior of various electronic devices, to analyze and design Electronic Circuits and subsystems using these devices. By learning this subject, students become familiar with the device parameters, the variation of the parameters within a given type and with a change of temperature. The effect of inevitable internal capacitances in circuits, the effect of input and output resistances and loading on circuit operations will be studied. These considerations are of atmost importance to the students. Since the circuits to be designed must function properly and reliably in the physical world, rather than under hypothetical or ideal circumstances, proper care should be taken in design.

#### 7.5.2 SCOPE

The Electronic Devices and Circuits subject is considered as foundation course for Electronics, Electrical, Computer Science Engineers etc. This course covers a syllabus from solid state physics to design of amplifiers, which make the students to familiarise to construct the basic building blocks required for audio and power amplifier design.

#### 7.5.3 PREREQUISITES

Basic concepts of Solid State Physics is required.

#### 7.5.4.1 SYLLABUS - JNTU

#### UNIT I P-N JUNCTION DIODE OBJECTIVE

Characteristics of Mathematical treatment of Junction diode characteristics, P-N Junction diode, Introduction to special semiconductor diode like Zener diode etc. Introduction to special semiconductor diodes like tunnel diode, SCR, Varactor diode and Semiconductor Photo Diode.

#### SYLLABUS

**P-N JUNCTION DIODE:**Qualitative Theory of p-n junction, p-n junction a diode, diode equation, Volt-ampere characteristics, Temperature dependence of VI characteristic, ideal versus practical - Resistance levels (Static and Dynamic), Transition and Diffusion Capacitances, Diode equivalent circuits, Load line analysis, Breakdown mechanisms in semi conductor diodes, Zener diode characteristics.

**SPECIAL PURPOSE ELECTRONIC DEVICES:**Principle of operation and characteristics of Tunnel diode (with the help of Energy Band Diagram) and Varactor diode, SCR, and Semiconductor Photo Diode.

#### UNIT II

### RECTIFIERS AND FILTERS OBJECTIVE

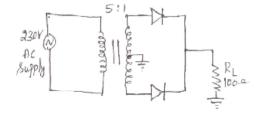

Basics of Half wave, Full wave and bridge rectifiers. Rectifiers with filters and the voltage regulation using zener diode.

#### SYLLABUS

The p-n junction as Rectifier, Half wave rectifier, Full wave rectifier, Bridge rectifier, Harmonic components in a rectifier circuit, Inductor filters, Capacitor filters, L-section filters, -section filters, Comparison of filters, Voltage regulation using Zener diode.

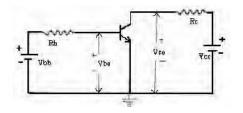

#### UNIT III BIPOLAR JUNCTION TRANSISTOR OBJECTIVE

Fundamentals of BJT, Construction Principles, operation and Characteristic curves in different configurations of transistors .Small signal equavalent circuits of BJT.The unit junction transistor

#### SYLLABUS

The junction transistor, Transistor current components, Transistor as an Amplifier, Transistor construction, BJT operation, BJT symbol, Common base, Common Emitter and Common collector configurations, Limits of Operation, BJT specifications.BJT Hybrid model, Determination of h-parameters from transistor characteristics. Comparison of CB, CE and CC amplifier configurations.UJT and Characteristics.

#### UNIT IV TRANSISTOR BIASING AND STABILISATION OBJECTIVE

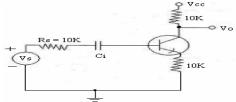

Biasing and stabilization techniques for BJT. Amplifier configurations of BJT using h-parameters.

#### SYLLABUS

Operation point, the DC and AC load lines, Need for biasing, Fixed bias, Collector feedback bias, Emitter feedback bias, Collector-Emitter feedback bias, Voltage divider bias, Bias stability, Stabilization factors, Stabilization against variation in  $V_{BE}$  and , Bias compensation using diodes and transistors, Thermal runaway, Thermal stability. Analysis of a transistor amplifier circuit using h-parameters.

### UNIT V FIELD EFFECT TRANSISTOR AND FET AMPLIFIERS

#### **OBJECTIVE**

Fundamentals of FET, Construction Principles, operation and Characteristic curves of transistors.Small signal equivalent circuits of FET. Amplifier configurations using FET.

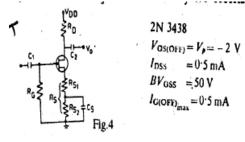

#### SYLLABUS

**FIELD EFFECT TRANSISTOR**: The junction field effect transistor (Construction, principle of operation, symbol) - Pinch-off voltage - Volt-ampere characteristics, The JFET small signal model, MOSFET (construction, principle of operation, symbol), MOSFET characteristics in enhancement and depletion modes. **FET AMPLIFIERS**: FET common source amplifier, Common drain amplifier, Generalized FET amplifier, Biasing FET, FET as voltage variable resistor, Comparison of BJT and FET.

#### 7.5.4.2 SYLLABUS - JNTU- GATE

#### UNIT I

Simple diode circuits, Characteristics of Tunnel Diode, Varactor diode, SCR, and semiconductor photo diode.

#### UNIT II

Rectifiers, Filters, Power supplies

#### UNIT III

BJTs, Characteristics, Equivalent circuits, large and small signals.

#### UNIT IV

Biasing and bias stability of transistor, Single-transistor configurations, Amplifiers of BJT, Analysis of amplifier.frequency response of amplifiers.

#### UNIT V

JFETs and MOSFETs, Equivalent circuits, large and small signals. Amplifiers of FET, Analysis of amplifier; frequency response of amplifiers

#### 7.5.4.3 SYLLABUS - IES

#### UNIT I

Simple diode circuits, Characteristics of Tunnel Diode, Varactor diode, SCR, and semiconductor photo diode.

#### UNIT II

Rectifiers, Filters, Power supplies

#### UNIT III

BJTs, Characteristics, Equivalent circuits, large and small signals.

#### UNIT IV

Biasing and bias stability of transistor, Single-transistor configurationsAmplifiers of BJT, Analysis of amplifier; frequency response of amplifiers.

#### UNIT V

JFETs and MOSFETs, Equivalent circuits, large and small signals. Amplifiers of FET, Analysis of amplifier; frequency response of amplifiers.

#### 7.5.5 SUGGESTED BOOKS

#### **TEXTBOOKS**

- T1. Millman's Electronic Devices and Circuits J. Millman, C.C.Halkias, and Satyabrata Jit, 2 Ed., 1998, TMH.

- T2. Electronic Devices and Circuits Mohammad Rashid, Cengage Learing, 2013

- T3. Electronic Devices and Circuits David A. Bell, 5 Ed, Oxford

#### **REFERENCES:**

- R1. Integrated Electronics J. Millman and Christos C. Halkias, 1991 Ed., 2008, TMH.

- R2. Electronic Devices and Circuits R.L. Boylestad and Louis Nashelsky, 9 Ed., 2006, PEI/PHI.

- R3. Electronic Devices and Circuits B. P. Singh, Rekha Singh, Pearson, 2Ed, 2013.

- R4. Electronic Devices and Circuits K. Lal Kishore, 2 Ed., 2005, BSP.

- R5. Electronic Devices and Circuits Anil K. Maini, Varsha Agarwal, 1 Ed., 2009, Wiley India Pvt. Ltd.

- R6. Electronic Devices and Circuits S.Salivahanan, N.Suresh Kumar, A.Vallavaraj, 2 Ed., 2008, TMH.

#### 7.5.6 WEBSITES

- 1. www.mit.com

- 2. www.nptel.iitm.ac.in

- 3. www.faadooengineers.com

- 4. www.iete.org

- www.ieee.org

www.pearsonhighered.com

- 7. en.wikipedia.org/wiki/Electronics

#### 7.5.7 EXPERTS' DETAILS

#### **INTERNATIONAL**

- 1. Prof. Trevor J.Trarnton, Director of Center for Solid State Electronics Research, Arizona State University, Tempe, USA Email: khan.tarik@asu.edu,

- 2. Dr. Manwong, Dept. of EEE, The Hong Kong University of Science & Technology, Kowloon, Hongkong. Email: eemwong@ee.ust.hk

- 3. Dr. I.Irisawa, MIRAI-ASET, Kawasaki, Japan. Email: irisawa@mirai.aist.go.jp

- 4. Dr. Stephen Pearton University of Florida, Gainesville, USA, Email: spear@mse.ufl.edu

#### NATIONAL

- 1 Dr. G.S.N. Raju Professor Andhra University

- 2. Prof. K.Venkat Rao, Principal, GMR Institute of Engineering and Technology Rajam Vijayanagaram District, A.P.

- 3. Dr. P.S. Murthy Professor, Dept.of ECE, Indian Institute of Technology, Kanpur.

#### REGIONAL 1. Dr. K.Lal Kishore, Registrar, JNTU, Kukatpally,

#### 7.5.8 JOURNALS

#### **INTERNARIONAL**

- 1. International Journal of Electornics Taylor & Francis Ltd.

- 2. IEEE, Transactions on Electron Devices.

- 3. IEEE, Transactions on Circuits and systems.

- 4. IEEE, Transactions on Power electronics

#### NATIONAL

- 1. IETE Journal

- 2. ISOI Journal

- 3. Journal on Institution of Engineers

- 4. IETE Journal of Education

- 5. IETE Journal of Research

#### 7.5.9 FINDINGS AND DEVELOPMENTS

- 1. Gate Leakage Mechanisms in AlGaN/GaN and AlInN/GaN HEMTs: Comparison and Modeling. IEEE Transactions on Electronic Devices, Vol.60, No. 10, October 2013.

- 2. Resistance and Threshold Switching Voltage drift behaviour, IEEE Transactions on Electronic Devices, Vol.58, No. 3, March 2011.

- 3. Interdigit 4H-Sic vertical schottky diode for Beta voltaic applications, IEEE Transactions on Electronic Devices, Vol.58, No. 3, March 2011.

- 4. A model -based approach for subthreshold operations, IEEE Transactions on Electronic Devices, Vol.58, No. 3, March 2011.

- 5. Full replacement Gate process for MOSFETs fabrications, IEEE Transactions on Circuits and Systems, Vol.58, No. 3, March 2011..

- 6. Effects of Variation in the source Doping concetration, IEEE Transactions on Circuits and Systems, Vol.58, No.3, March 2011.

- 7. Simulation of devices for each epitasial structure for 50nm gate length devices, IEEE Transactions on Circuits and Systems, Vol.58, No.3, March 2011..

- 8. Thermal stress analysis inside Phase Change Memory (PCM) cell using the measured properties, IEEE Transactions on Circuits and Systems, Vol.58, No.3, March 2011.

- 9. Subthreshold Electron Mobility in SoI MOSFETs, Tarik Khan, Dragica Vasileska, Member, IEEE and Trevor J. Thornton, Member, IEEE. Prof. Trevor J. Thornton, Dept of EEE. IEEE Transactions on Electron Devices, Vol.52, No.7, July 05.

- Effects of Substrate Doping on Linearly Extrapolated Threshold voltage of Symmetrical DG MOS Devices, - Xuejie Shi and Dr. ManWong, Dept of EEE. IEEE Transactions on Electron Devices, Vol.52, No.7, July 05.

- 11. On the origin of Increase in substrate current and Impact Ionization Efficiency in strained-si n-and p-MOSFETs T. Irisarva, T. Numata, N. Sugiyama and S-I. Takagi. IEEE Transactions on Electron Devices, Vol.52, No.7, July 05.

## **Session Plan**

| SI.<br>No. | Topics in JNTU<br>syllabus                                                | Modules and Sub modules                                                                                                            | Lecture | Suggested books           | Remarks     |

|------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------|-------------|

| UNIT I     |                                                                           |                                                                                                                                    |         |                           |             |

| 1          | Objective and relevance<br>Prerequisite and background<br>Suggested books |                                                                                                                                    | L1      |                           |             |

| 2          | P –N Junction Diode                                                       | Review of semiconductor<br>physics<br>Electrons and holes in an<br>intrinsic semiconductor<br>Conductivity of semiconductor        | L2      | T1-Ch5, R4-Ch2<br>R2-Ch1  | GATE<br>IES |

|            |                                                                           | Carrier concentration in an<br>intrinsic semiconductor<br>Donor and acceptor impurities<br>Charge densities in an<br>semiconductor | L3      | T1-Ch5, R4-Ch2<br>R2-Ch1  | GATE<br>IES |

| 3          | Qualitative Theory of p-n junction                                        | junction T1-Ch5, R<br>The p-n junction as a diode L4-L5                                                                            |         | T1-Ch5, R2-Ch1<br>R4-Ch3, | GATE<br>IES |

| 4          | V-I characteristics of<br>p-n diode                                       | V-I characteristics of p-n diode<br>Diode resistance                                                                               | L6      |                           | GATE<br>IES |

| 5          | Temperature<br>dependence of V-I<br>characteristics                       | Temperature dependence of V-I characteristics                                                                                      |         | T1-Ch5, R4-Ch3            | GATE<br>IES |

| 6         | Transition<br>capacitance                                                                                     | Space charge or transition capacitance                                       |        |                           |             |  |

|-----------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------|---------------------------|-------------|--|

|           |                                                                                                               | Step graded junction and                                                     |        | T1-Ch5, R4-Ch3            | GATE<br>IES |  |

| 7         | Diffusion capacitance                                                                                         | Diffusion capacitance<br>p-n diode switching times                           |        |                           |             |  |

| 8         | Breakdown<br>mechanism in<br>semiconductor diode<br>Zener diode<br>characteristics                            | Breakdown mechanism in<br>semiconductor diode<br>Zener diode characteristics | L9     | T1-Ch5, R4-Ch3<br>R2-Ch1, | GATE<br>IES |  |

| 9         | Principle of operation<br>and characteristics of<br>Tunnel diode (with<br>the help of Energy<br>Band Diagram) | Characteristics of Tunnel Diode                                              | L10    | T1-Ch5, R2-16             | GATE<br>IES |  |

| 10        | Varactor diode                                                                                                | Characteristics of Varactor diode                                            | L11    | T1-Ch5, R2-16             | GATE<br>IES |  |

| 11        | SCR                                                                                                           | Characteristics of SCR<br>Applications of SCR                                | L12    | T1-Ch5, R2-16             | GATE<br>IES |  |

| 12        | Semiconductor Photo<br>Diode.                                                                                 | LED characteristics<br>Photo diode characteristics                           | L13    | T1-Ch19, R2-16            | GATE<br>IES |  |

| UNIT – II |                                                                                                               |                                                                              |        |                           |             |  |

| 9         | Half wave rectifier                                                                                           | Half wave rectifier<br>Ripple factor<br>Average voltage,                     | L14-15 | T1-Ch6, R2-Ch2            | GATE        |  |

|           |                                                                                                               | RMS voltage, TUF,<br>Voltage regulation and<br>Rectification efficiency      | L14-13 | R4-Ch3                    | IES         |  |

| SI.<br>No. | Topics in JNTU<br>syllabus                                         | Modules and Sub modules                                                                                                                    | Lecture | Suggested books             | Remark<br>s |

|------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|-------------|

| 10         | Full wave rectifier                                                | Full wave rectifier<br>Ripple factor<br>Average voltage,                                                                                   |         | T1-Ch6,                     | GATE        |

|            |                                                                    | L1<br>RMS voltage,TUF,<br>Voltage regulation and<br>Rectification efficiency                                                               |         | R2-Ch2<br>R4-Ch3            | IES         |

| 11         | Bridge rectifier                                                   | RMS voltage,<br>L18 R2-Cl<br>TUF,                                                                                                          |         | T1-Ch6,<br>R2-Ch2<br>R4-Ch3 | GATE<br>IES |

| 12         | Harmonic<br>components in<br>rectifier circuits<br>Inductor filter | Harmonic components in<br>rectifier circuits<br>Cancellation of fundamental<br>components and advantage of<br>filtering<br>Inductor filter | L19     | T1-Ch6,<br>R4-Ch3           | GATE<br>IES |

| 13         | Capacitor filter                                                   | Capacitor filter     L20       Average voltage     L20       Ripple factor     Problems                                                    |         | T1-Ch6,<br>R4-Ch3           | GATE<br>IES |

| 14         | L-section filter                                                   | L-section filter<br>Average voltage<br>Ripple factor<br>Problems                                                                           | L21     | T1-Ch6,<br>R4-Ch3           | GATE<br>IES |

| 1    | 5 1                         | I - section filter                      | $\Pi$ - Section filter          |         | T1-Ch6,         | GATE   |

|------|-----------------------------|-----------------------------------------|---------------------------------|---------|-----------------|--------|

| Mult |                             | Aultiple $\Pi$ - section                | Multiple $\Pi$ - section filter | L22     |                 | 150    |

|      | filter                      |                                         |                                 |         | R4-Ch3          | IES    |

|      |                             |                                         |                                 |         |                 |        |

| 1    |                             | Comparison of<br>arious filter circuits | Comparison of various filters   |         | T1-Ch6,         | GATE   |

|      |                             | n terms of ripple                       |                                 | L23     |                 |        |

|      |                             | actors                                  |                                 |         | R4-Ch3          | IES    |

|      |                             |                                         |                                 |         |                 |        |

| 1    |                             | imple circuit of a                      | Simple circuit of a regulator   |         |                 |        |

|      |                             | egulator using zener<br>liode           | using zener diode               |         | R2-Ch19,        | GATE   |

|      | Ľ                           | noue                                    | Problems                        | L24     | T1-Ch6          | IES    |

|      |                             |                                         |                                 |         | 11-010          | 125    |

|      |                             |                                         |                                 |         |                 |        |

|      |                             |                                         |                                 |         |                 |        |

| -    | 18                          | Junction transistor,                    | Junction Transistor,            |         |                 |        |

|      | Transistor<br>construction, |                                         |                                 |         |                 |        |

|      |                             |                                         | Transistor construction, BJT    |         |                 |        |

|      |                             |                                         | operation, BJT Symbol           | L25     | T1-Ch7, R2-Ch3  | GATE   |

|      |                             | BJT operation,                          |                                 |         |                 |        |

|      |                             | BJT Symbol,                             |                                 |         |                 |        |

| F    | 19                          | Transistor as a                         | The transistor as a amplifier   |         |                 |        |

|      |                             | amplifier                               |                                 | L26     | T1-Ch7, R2-Ch3  | GATE   |

|      |                             |                                         | Transistor construction         |         |                 |        |

| F    | 20                          | Transistor Current                      | The detailed study of currents  | 1.27    |                 | CATE   |

|      |                             | components                              | in a transistor                 | LZ7     | T1-Ch7, R2-Ch3  | GATE   |

| ŀ    | 21                          | СВ                                      | Characteristics of BJT          |         |                 |        |

|      | 21                          |                                         |                                 |         | R4-Ch4, T1-Ch7  | GATE   |

|      |                             |                                         | CB-configuration                | L28     |                 |        |

|      |                             |                                         | Input-output characteristics    |         | R2-Ch3,         | IES    |

|      |                             |                                         | input output characteristics    |         |                 |        |

| Ī    | 22                          | CE                                      | CE-configuration                |         | R4-Ch4, T1-Ch7  | GATE   |

|      |                             |                                         | Input-output characteristics    | L29     | R2-Ch3,         | IES    |

|      |                             |                                         |                                 |         | N2-CH3,         | 125    |

| Γ    | SI.                         | Topics in JNTU                          | Modules and Sub modules         | Lecture | Suggested books | Remark |

|      | No.                         | syllabus                                | yllabus                         | Lettere |                 | S      |

| ╞    | 23                          | СС                                      | CC-configuration                |         | R4-Ch4, T1-Ch7  | GATE   |

|      |                             |                                         |                                 | L30     |                 |        |

|      |                             | 1                                       | Input-output characteristics    |         | R2-Ch3          | IES    |

|      |                             |                                         |                                 |         |                 | IL3    |

| 24 |                                                                         | Relations between Alpha and<br>Beta, GammaL31T1-Ch7, R2,Ch3                                              |     | T1-Ch7, R2,Ch3                           | GATE<br>IES |

|----|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|------------------------------------------|-------------|

| 25 | Limits of operation<br>and BJT specification                            | Limits of operation and BJT<br>specification L32 T1-Ch7, R2,Ch                                           |     | T1-Ch7, R2,Ch3                           | GATE<br>IES |

| 26 | BJT Hybrid model                                                        | Small signal low frequency<br>transistor amplifier circuits<br>L<br>Two-port devices and hybrid<br>model |     | T1-Ch9,<br>R2-Ch5, R4-Ch5                | GATE<br>IES |

| 27 | Determination of h-<br>parameters from<br>transistor<br>characteristics | ansistor ampliner using in L34                                                                           |     | T1-Ch9,<br>R2-Ch5, R4-Ch5                | GATE<br>IES |

| 28 | Comparison of CB, CE<br>and CC amplifier<br>configurations.             | Comparison of CB, CE and CC amplifier configurations.                                                    | ,   |                                          | GATE<br>IES |

| 29 | The UJT and charactersitics                                             | Construction and<br>Characteristics of Uni<br>junction transistor.                                       | L36 | T1-Ch14, R2-<br>Ch21                     | GATE<br>IES |

|    |                                                                         | UNIT-IV                                                                                                  |     |                                          |             |

| 26 | Operating point<br>The DC and AC load<br>lines<br>Need for biasing      | Biasing: DC and AC load lines<br>Operating point<br>Criteria for fixing operating<br>point               | L37 | R2-Ch4,<br>GA<br>T1-Ch8<br>IE<br>R4-Ch6, |             |

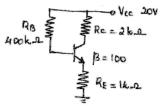

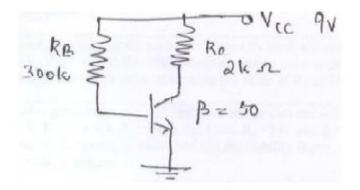

| 27 | Fixed bias                                                              | Fixed bias circuit Calculation of Q-point L38 Procedure to find Stability factor Problems                |     | R2-Ch4,<br>T1-Ch8<br>R4-Ch6,             | GATE<br>IES |

|    |                                  |                                                      |                       |         | 1    |

|----|----------------------------------|------------------------------------------------------|-----------------------|---------|------|

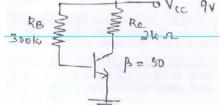

| 28 | Collector feedback bias          | Collector to base bias<br>Calculation of Q-point     | R2-Ch4,<br>L39 T1-Ch8 |         | GATE |

|    |                                  |                                                      |                       |         | GAIL |

|    |                                  | Procedure to find Stability factor                   |                       |         | IES  |

|    |                                  | Problems                                             |                       | 14-010, |      |

| 29 | Emitter feedback<br>bias,        | Emitter feedback bias circuit                        |                       | R2-Ch4, |      |

|    | ,                                | Calculation of Q-point                               | L40                   | T1-Ch8  | GATE |

|    |                                  | Procedure to find Stability factor                   | L40                   | R4-Ch6, | IES  |

|    |                                  | Problems                                             |                       | 14-010, |      |

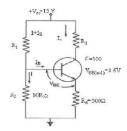

| 30 | Collector-Emitter                | Collector-Emitter feedback bias                      |                       |         |      |

|    | feedback bias                    | circuit                                              |                       | R2-Ch4, | CATE |

|    |                                  | Calculation of Q-point                               | L41                   | T1-Ch8, | GATE |

|    |                                  | Procedure to find Stability factor                   |                       | R4-Ch6  | IES  |

|    |                                  | Problems                                             |                       |         |      |

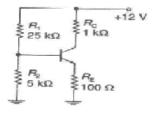

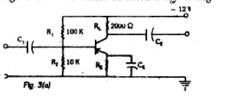

| 31 | Voltage divider bias,            | Voltage divider bias circuit                         |                       |         |      |

|    | Bias Stability                   | Calculation of Q-point                               |                       | R2-Ch4, | GATE |

|    |                                  | Procedure to find Stability factor                   | L42                   | T1-Ch8  | IES  |

|    |                                  |                                                      |                       | R4-Ch6, |      |

|    |                                  | Problems                                             |                       |         |      |

| 32 | Stabilization factors            | Stabilization against variations                     |                       |         |      |

|    | Stabilization against            | in $V_{\text{BE}}$ and $\beta$ for self bias circuit |                       | R2-Ch4, | GATE |

|    | variation in V <sub>BE</sub> and | Stability factor S <sup>1</sup> and S <sup>11</sup>  | L43                   | T1-Ch8  | IES  |

|    | Beta,                            | Problems                                             |                       | R4-Ch6, | IE3  |

|    |                                  | Bias compensation                                    |                       |         |      |

| 33 | Compensation                     | Compensation against variation                       |                       | R2-Ch4, | CATE |

|    | techniques using<br>diodes and   | in V <sub>BE</sub>                                   | L44                   | T1-Ch8  | GATE |

|    | transistors.                     | Compensation against variation in I <sub>co</sub>    |                       | R4-Ch6  | IES  |

|    |                                  |                                                      |                       |         |      |

| 34         | Thermal runway<br>Thermal Stability                                                            | Condition to avoid thermal runway                                                                                                                                                                                                                       | L45          | R2-Ch4,<br>T1-Ch8<br>R4-Ch6    | GATE<br>IES |

|------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------|-------------|

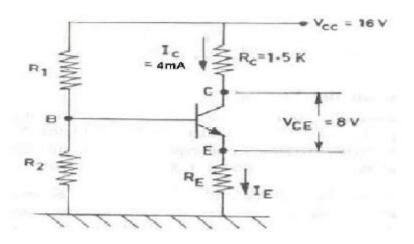

| 35         | Analysis of a<br>transistor amplifier<br>circuit using<br>h-parameters                         | Measurement of h-parameters<br>for CB, CE, CC<br>(Voltage gain and current gain<br>Input and output impendence)<br>h-parameters<br>Approximate analysis of CB CE<br>and CC amplifier circuits<br>Analysis of various amplifier<br>circuits,<br>Problems | L46 –<br>L47 | T1-Ch8,<br>R2-Ch5, R4-Ch5      | GATE<br>IES |

| SI.<br>No. | Topics in JNTU<br>syllabus                                                                     | Modules and Sub modules                                                                                                                                                                                                                                 | Lecture      | Suggested books                | Remark<br>s |

|            | I                                                                                              | UNIT V                                                                                                                                                                                                                                                  | I            |                                |             |

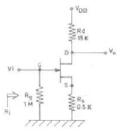

| 36         | The junction field<br>effect transistor<br>(Construction<br>principle of<br>operation, symbol) | JFET construction and its static<br>characteristics, pinch-off<br>voltage,<br>CG, CD and CS configurations                                                                                                                                              | L48-49       | R4-Ch8,<br>T1, Ch12<br>R2-Ch5, | GATE<br>IES |

| 37         | Pinch-off Voltage -<br>Volt-Ampere<br>characteristics                                          | Pinch-off Voltage,ON resistanceR4-Ch8,rd(ON), Pinch-off region,theL50T1, Ch12region before Pinch-off, theL50R2-Ch6,                                                                                                                                     |              | T1, Ch12                       | GATE<br>IES |

| 38         | The JFET small signal model                                                                    | Transconductance(g <sub>m</sub> ),Drain<br>Resistance(r <sub>d</sub> ) L51 T1-Ch12                                                                                                                                                                      |              | R4-Ch8,<br>T1-Ch12<br>R2-Ch6   | GATE<br>IES |

| 39         | MOSFET<br>(construction<br>principle of<br>operation, symbol),                                 | MOSFET (construction principle of operation, symbol),                                                                                                                                                                                                   | L52          | R4-Ch8,<br>T1-Ch12<br>R2-Ch6   | GATE<br>IES |

| 40 | MOSFET<br>characteristics in<br>enhancement and<br>depletion modes | MOSFET characteristics in R4-Ch8,<br>enhancement and depletion<br>modes L53 T1-Ch12<br>R2-Ch6                                                                                      |        | T1-Ch12            | GATE<br>IES |

|----|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|-------------|

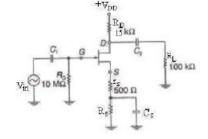

| 41 | FET common source<br>amplifier                                     | Analysis of a FET Amplifier using<br>small signal model (common<br>source),Voltage gain,Input<br>admittance,Input capacitance,<br>Output Resistance.                               | L54    | T1-Ch12<br>R2-Ch8  | GATE<br>IES |

| 42 | Common drain<br>amplifier                                          | Analysis of a FET Amplifier using<br>small signal model (common<br>drain) ,Voltage gain,Input<br>admittance, Output admittanceT1-Ch12<br>R2-Ch8                                    |        |                    | GATE<br>IES |

| 43 | Generalized FET<br>amplifier                                       | Generalized FET<br>amplifier,Output from the<br>Drain,The CS Amplifier with an<br>unbypassed source<br>resistance,The CG Amplifier ,The<br>output from the source,CD<br>Amplifier. | L56-57 | T1-Ch12<br>R2-Ch8  | GATE<br>IES |

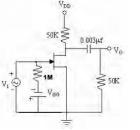

| 44 | Biasing FET                                                        | Biasing FET<br>Fixed Bias,<br>Potential divider,                                                                                                                                   | L58    | T1-Ch12<br>R2-Ch7  | GATE<br>IES |

| 45 | FET as voltage<br>variable resistor                                | FET as voltage variable     T1-Ch12       resistor,Applications of VVR.     L59                                                                                                    |        | T1-Ch12            | GATE<br>IES |

| 48 | Comparison of BJT<br>and FET                                       | Comparison of BJT and FET                                                                                                                                                          | L60    | T1-Ch12<br>R2-Ch11 | GATE<br>IES |

## **Question Bank**

## **UNIT-I**

| 1.       |           | Explain the formation of depletion region in an open circuited pn junction with neat sketches.<br>The voltage across a silicon diode at room temperature of 300oK is 0.7V when 2mA<br>current flows through it. If the voltage increases to 0.75V, calculate the diode current.                                                                                                                                                                                                                       |           |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          |           | current nows through it. If the voltage increases to 0.75 v, calculate the diode current.                                                                                                                                                                                                                                                                                                                                                                                                             | (Nov13)   |

| 2.       | i)        | Draw the basic structure of Varactor diode and Explain its operation.                                                                                                                                                                                                                                                                                                                                                                                                                                 | (110/20)  |

|          | ii)       | Explain the V-I characteristics of a Tunnel Diode.                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (Nov13)   |

| 3.<br>4. | i)<br>ii) | Obtain an expression for the current components in a PN junction diode.<br>Two identical junction diodes are connected back to back whose VIcharacteristics is Is=0.1uA; Vt and $\eta$ =2 are connected .The supply voltageis 15V and the value of the RL=100K.Find the voltage each diode and current in the circuit.<br>In a Zener diode regulator nomial Vi=40V, imax V =45V, imin V =35V, rz=5 $\Omega$ , 1min I =0mA, 1max I =100mA,, z max I =400mA and z min I =10mA. Find z max P, Ro and Sv. |           |

|          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (Nov13)   |

| 5.       | i.        | Sketch V-I Characteristics of a PN diode for the following conditions:<br>i. $R_f = 0$ , $V\gamma = 0$ , $R_r = \infty$                                                                                                                                                                                                                                                                                                                                                                               |           |

|          |           | ii. $R_f = 0$ , $V\gamma = 0.6V$ , $R_r = \infty$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|          |           | iii. $R_f = Non$ -zero fixed value, $V\gamma=0$ , $R_r = \infty$<br>iv. $R_f = Non$ -zero fixed value, $V\gamma=0.6V$ , $R_r = \infty$<br>Where $V\gamma$ is the cut -in voltage, $R_f$ is the forward dynamic resistance & $R_r$ is the reverse dynamic                                                                                                                                                                                                                                              | 2         |

|          | ii.       | resistance of the diode.<br>Find the voltage drop across each of the silicon diodes shown in Figure .1 at room temperature. As that rverse saturation currnt flows in th circuit and the magnitude of the revrsbreakdown voltage is than 5V?                                                                                                                                                                                                                                                          | sume      |

|          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (Dec12)   |

| 6.       | i.<br>ii. | Draw the structure and two -transistor model of SCR, explain various methods of triggering an SC With neat sketches, explain the principle of operation of Schottky Barrier Drode.                                                                                                                                                                                                                                                                                                                    | CR.       |

|          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Dec12)    |

| 7.       | i.<br>ii. | With neat sketches and necessary expressions describe V-I characteristics of a semiconductor photo<br>With neat sketches and necessary expressions describe the operation of Varactor diode?                                                                                                                                                                                                                                                                                                          | to diode? |

|          |           | (No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | v 11)     |

| 8.       | i.<br>ii. | Draw the firing characteristics of SCR and briefly explain it.<br>Define the following with respect to SCR<br>a. Forward break over voltage<br>b. Reverse break over voltage<br>c. Holding current<br>d. Goto triggor current                                                                                                                                                                                                                                                                         |           |

|          |           | d. Gate trigger current. (No                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | v 11)     |

| 0        | :         | With next anarow hand diagrams, avalain the V L characteristics of Tunnel diada. Also discuss the                                                                                                                                                                                                                                                                                                                                                                                                     | nogativa  |

- 9. i. With neat energy band diagrams, explain the V-I characteristics of Tunnel diode. Also discuss the negative resistance property of tunnel diode. (Nov 11)

- ii. With neat sketches explain the operation of Schottky Barrier Diode.

- 10. i. With neat energy band diagrams, explain the V-I characteristics of Tunnel diode. Also discuss the negative resistance property of tunnel diode.

- Draw the two-transistor model of SCR and explain its operation. (Nov 11) ii.

- 11. i. What is Fermi level? By indicating the position of Fermi level in intrinsic, n-type and p- type semicon ductor, explain its significance in semiconductors?

- ii. Sketch V-I characteristics of a PN diode for the following conditions:

- a. Rf = 0, V = 0,  $\mathbf{Rr} = \infty$

- b. Rf = 0, V = 0.6V,  $\mathbf{Rr} = \infty$

V = 0,  $Rr = \infty$ c. Rf = Non-zero, fixed value,

V = 0.6V,  $Rr = \infty$ d. Rf = Non-zero, fixed value,

Where VfA is the cut-in voltage, Rf is the forward dynamic resistance & Rr is the reverse dynamic resistance of the diode. (Nov 11)

- 12. i. What do you understand about the depletion region at a PN junction, with the help of necessary diagrams and derive expression for barrier potential.

- ii. Derive the expression for transition capacitance, CT of a PN diode. (Nov 11)

- 13.i. With the help of necessary sketches explain the potential distribution in an open circuited PN junction. With the help of V-I Characteristics, explain the operation of a PN Diode under Forward bias and Reverse ii. bias. (Nov 11)

- 14. i. Explain Avalanche and Zener break down mechanisms in semiconductors and compare them?

- For the Zener diode circuit shown in Figure.1, determine VL, VR, IZ & R (Nov 11) ii.

- Derive an expression for total diode current starting from Boltzmann relationship in terms of the applied 15. i. voltage.

- The reverse saturation current of a silicon p n junction diode at an operating temperature of  $27^{0}$ C is 50 ii. nA. Compute the dynamic forward and reverse resistances of the diode for applied voltages of 0.8 V and -0.4 V respectively. (Nov 10)

- Explain the operation of silicon p n junction diode and obtain the forward bias and reverse bias Volt 16. i. Ampere characteristics.

- ii. Obtain the transition capacitance  $C_T$  of a junction diode at a reverse bias voltage of 12 V if  $C_T$  of the diode is given as 15 PF at a reverse bias of 8 V. Differentiate between transition and diffusion capacitances.

- 17. Difference between

- i. Static and dynamic resistances of a p - n diode.

- Transition and Diffusion capacitances of a p n diode. ii.

- iii. Volt Ampere characteristics of a single silicon p n diode and two identical silicon p- n diodes connected in parallel.

- iv. Avalanche and zener break down mechanisms.

- 18. i. Define the following terms for a PN diode a) Dynamic resistance b) Load line c) Difference capacitance d) Reverse saturation current

- A reverse bias voltage of 90V is applied to a Germanium diode through a resistance R. The reverse ii. saturation current of the diode is 50 mA at an operating temperature of 250C. Compute the diode current and voltage for a)  $R = 10 M \square$ b) R = 100 K

- 19. Describe the following briefly:

- Principle of operation of a photodiode. i.

- ii. Energy band structure and V I characteristics of a tunnel diode.

- (Nov 10)

- (Nov 10)

- (Nov 10)

(Nov 10)

| 20. i.<br>ii. | What is schottky effect? Elaborate schottky effect for the functioning of a schottky Barrier Describe the construction, principle of operation and performance characteristics of a S Rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 21.           | Explain the principle of operation of the following devices:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                      |

| i.<br>ii.     | Schottky Barrier diode<br>Tunnel diode through Energy band diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (Nov 10)                             |

| 22.           | Explain how a variable capacitance can be built using a varactor diode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (Nov 10)                             |

| 23. i.<br>ii. | Explain about diffusion capacitance in detail.<br>Derive an expression for diffusion capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (May 09)                             |

| 24. i<br>ii.  | Define Mass Action Law<br>Explain N type & P type Semiconductors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (May 09)                             |

| 25. i.<br>ii. | Explain about semiconductor, Insulator & Conductor with neat sketch.<br>State the Einstein relationship for semiconductor. State paulis exclusion principle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (May 08)                             |

| 26. i.<br>ii. | Explain the volt ampere characteristics of PN diode.<br>Explain the temperature dependence of VI characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (May 08)                             |

| 27. i.<br>ii. | Explain about various current components in a forward biased p-n Junction diode.<br>Find the value of D.C. resistance and A.C resistance of a Germanium Junction diode at $25\mu$ A and at an applied voltage of 0.2V across the diode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 250 C with Io =<br>( <b>May 07</b> ) |

| 28. i.<br>ii. | Explain the formation of depletion region in an open-circuited p-n Junction with neat sketc A p-n Junction diode has a reverse saturation current of 30 $\mu$ A at a temperature of 125 temperature find the dynamic resistance for 0.2V bias in forward and reverse direction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

| 29.           | What do you understand by depletion region at p-n Junction? What is the effect of forv<br>biasing of p-n Junction on the depletion region? Explain with necessary diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ward and reverse<br>(May 07, 06)     |

| 30. i.        | Explain the process of break down of a p-n Junction diode due to<br>a. Avalanche effect<br>b. Zener effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                      |